This PDF is available at http://www.nap.edu/23561

Optimizing the Air Force Acquisition Strategy of Secure and Reliable Electronic Components: Proceedings of a Workshop

# DETAILS

62 pages | 8.5 x 11 | PAPERBACK ISBN 978-0-309-44518-4 | DOI: 10.17226/23561

# **AUTHORS**

**BUY THIS BOOK**

FIND RELATED TITLES

Committee on Optimizing the Air Force Acquisition Strategy of Secure and Reliable Electronic Components: A Workshop; Air Force Studies Board; Division on Engineering and Physical Sciences; National Academies of Sciences, Engineering, and Medicine

# Visit the National Academies Press at NAP.edu and login or register to get:

- Access to free PDF downloads of thousands of scientific reports

- 10% off the price of print titles

- Email or social media notifications of new titles related to your interests

- Special offers and discounts

Distribution, posting, or copying of this PDF is strictly prohibited without written permission of the National Academies Press. (Request Permission) Unless otherwise indicated, all materials in this PDF are copyrighted by the National Academy of Sciences.

Copyright © National Academy of Sciences. All rights reserved.

# Optimizing the Air Force Acquisition Strategy of Secure and Reliable Electronic Components

Proceedings of a Workshop

Committee on Optimizing the Air Force Acquisition Strategy of Secure and Reliable Electronic Components: A Workshop

Air Force Studies Board

Division on Engineering and Physical Sciences

*The National Academies of* SCIENCES • ENGINEERING • MEDICINE

> THE NATIONAL ACADEMIES PRESS Washington, DC www.nap.edu

# THE NATIONAL ACADEMIES PRESS 500 Fifth Street, NW Washington, DC 20001

This activity was supported by Grant FA9550-14-1-0127 with the U.S. Air Force. Any opinions, findings, conclusions, or recommendations expressed in this publication do not necessarily reflect the view of any organization or agency that provided support for the project.

International Standard Book Number-13: 978-0-309-44518-4 International Standard Book Number-10: 0-309-44518-3 Digital Object Identifier: 10.17226/23561

Limited copies of this report are<br/>available from:Additional copies are available from:Air Force Studies Board<br/>National Research Council<br/>500 Fifth Street, NW<br/>Washington, DC 20001<br/>(202) 334-3111The National Academies Press<br/>500 Fifth Street, NW<br/>Keck 360<br/>Washington, DC 20001<br/>(800) 624-6242 or (202) 334-3313<br/>http://www.nap.edu

Copyright 2016 by the National Academy of Sciences. All rights reserved.

Printed in the United States of America

Suggested citation: National Academies of Sciences, Engineering, and Medicine. 2016. *Optimizing the Air Force Acquisition Strategy of Secure and Reliable Electronic Components: Proceedings of a Workshop.* Washington, DC: The National Academies Press. doi:10.17226/23561.

# *The National Academies of* SCIENCES • ENGINEERING • MEDICINE

The National Academy of Sciences was established in 1863 by an Act of Congress, signed by President Lincoln, as a private, nongovernmental institution to advise the nation on issues related to science and technology. Members are elected by their peers for outstanding contributions to research. Dr. Marcia McNutt is president.

The National Academy of Engineering was established in 1964 under the charter of the National Academy of Sciences to bring the practices of engineering to advising the nation. Members are elected by their peers for extraordinary contributions to engineering. Dr. C. D. Mote, Jr., is president.

The National Academy of Medicine (formerly the Institute of Medicine) was established in 1970 under the charter of the National Academy of Sciences to advise the nation on medical and health issues. Members are elected by their peers for distinguished contributions to medicine and health. Dr. Victor J. Dzau is president.

The three Academies work together as the National Academies of Sciences, Engineering, and Medicine to provide independent, objective analysis and advice to the nation and conduct other activities to solve complex problems and inform public policy decisions. The Academies also encourage education and research, recognize outstanding contributions to knowledge, and increase public understanding in matters of science, engineering, and medicine.

Learn more about the National Academies of Sciences, Engineering, and Medicine at www.national-academies.org.

# *The National Academies of* SCIENCES • ENGINEERING • MEDICINE

**Reports** document the evidence-based consensus of an authoring committee of experts. Reports typically include findings, conclusions, and recommendations based on information gathered by the committee and committee deliberations. Reports are peer reviewed and are approved by the National Academies of Sciences, Engineering, and Medicine.

**Proceedings** chronicle the presentations and discussions at a workshop, symposium, or other convening event. The statements and opinions contained in proceedings are those of the participants and are not necessarily endorsed by other participants, the planning committee, or the National Academies of Sciences, Engineering, and Medicine.

For information about other products and activities of the Academies, please visit nationalacademies.org/whatwedo.

# COMMITTEE ON OPTIMIZING THE AIR FORCE ACQUISITION STRATEGY OF SECURE AND RELIABLE ELECTRONIC COMPONENTS: A WORKSHOP

ROBERT H. LATIFF, R. Latiff Associates, *Chair* MICHAEL ETTENBERG, NAE,<sup>1</sup> Dolce Technologies CRAIG L. KEAST, MIT Lincoln Laboratory RANDAL W. LARSON, MITRE Corporation TERRY P. LEWIS, Raytheon Company CELIA MERZBACHER, Semiconductor Research Corporation BERNARD S. MEYERSON, NAE, IBM PAUL D. NIELSEN, NAE, Software Engineering Institute STARNES E. WALKER, University of Delaware

# Staff

JOAN FULLER, Director, Air Force Studies Board CARTER W. FORD, Program Officer MARGUERITE E. SCHNEIDER, Administrative Coordinator STEVEN G. DARBES, Research Assistant DIONNA C. ALI, Research Assistant

<sup>&</sup>lt;sup>1</sup> NAE, National Academy of Engineering.

## **AIR FORCE STUDIES BOARD**

DOUGLAS M. FRASER, Doug Fraser, LLC, Chair DONALD C. FRASER, NAE,<sup>1</sup> Charles Stark Draper Laboratory (retired), Vice Chair BRIAN A. ARNOLD, Peachtree City, Georgia ALLISON ASTORINO-COURTOIS, National Security Innovations, Inc. TED F. BOWLDS, The Spectrum Group STEVEN R.J. BRUECK, University of New Mexico FRANK J. CAPPUCCIO, Cappuccio and Associates, LLC BLAISE J. DURANTE, U.S. Air Force (retired) BRENDAN B. GODFREY, University of Maryland, College Park MICHAEL A. HAMEL, Lockheed Martin Space Systems Company DANIEL E. HASTINGS, Massachusetts Institute of Technology RAYMOND E. JOHNS, JR., Flight Safety International ROBERT H. LATIFF, R. Latiff Associates NANCY G. LEVESON, NAE, Massachusetts Institute of Technology MARK J. LEWIS, Institute for Defense Analyses Science and Technology Policy Institute ALEX MILLER, University of Tennessee OZDEN OCHOA, Texas A&M University RICHARD V. REYNOLDS, The VanFleet Group, LLC STARNES E. WALKER, University of Delaware DEBORAH WESTPHAL, Toffler Associates DAVID A. WHELAN, NAE, Boeing Defense, Space, and Security REBECCA WINSTON, Winston Strategic Management Consulting MICHAEL I. YARYMOVYCH, NAE, Sarasota Space Associates

# Staff

JOAN FULLER, Director ALAN H. SHAW, Deputy Director GEORGE COYLE, Senior Program Officer CARTER W. FORD, Program Officer ANDREW J. KREEGER, Program Officer DIONNA C. ALI, Research Assistant STEVEN G. DARBES, Research Assistant CHRIS JONES, Financial Manager MARGUERITE E. SCHNEIDER, Administrative Coordinator ADRIANNA HARGROVE, Senior Program Assistant/Financial Assistant

<sup>&</sup>lt;sup>1</sup> NAE, National Academy of Engineering.

# Acknowledgment of Reviewers

This proceedings has been reviewed in draft form by individuals chosen for their diverse perspectives and technical expertise, in accordance with procedures approved by the Report Review Committee. The purpose of this independent review is to provide candid and critical comments that will assist the institution in making its published proceedings as sound as possible and to ensure that it meets institutional standards for objectivity, evidence, and responsiveness to the study charge. The review comments and draft manuscript remain confidential to protect the integrity of the deliberative process. We wish to thank the following individuals for their review of this proceedings:

Kent E. Devenport, Kansas City National Security Campus, Department of Energy, Michael Fritze, Potomac Institute for Policy Studies, Butler W. Lampson, NAS/NAE, Microsoft Research, and Henry I. Smith, NAE, Massachusetts Institute of Technology.

Although the reviewers listed above have provided many constructive comments and suggestions, they were not asked to endorse the views presented at the workshop, nor did they see the final draft of the workshop proceedings before its release. The review of this workshop proceedings was overseen by Robert J. Hermann, NAE, Independent Consultant, Bloomfield, Connecticut, who was responsible for making certain that an independent examination of this workshop proceedings was carried out in accordance with institutional procedures and that all review comments were carefully considered. Responsibility for the final content of this proceedings rests entirely with the committee and the institution.

Optimizing the Air Force Acquisition Strategy of Secure and Reliable Electronic Components: Proceedings of a Workshop

# Contents

| 0\ | VERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1  | WORKSHOP CONTEXT AND ISSUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4  |

| 2  | WORKSHOP DISCUSSIONS AND KEY THEMES<br>Current Technological and Government Policy Challenges, 9<br>Current Technology Capabilities to Detect Fraud and Counterfeits, 12<br>Current Government Acquisition Challenges, 14<br>Options for Possible Business Models within the National Security Complex, 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9  |

| 3  | <ul> <li>PRESENTATION ABSTRACTS</li> <li>Day 1—March 16, 2016, 21</li> <li>Deputy Assistant Secretary of the Air Force for Science, Technology,<br/>and Engineering—David Walker (SES), 21</li> <li>Acting Deputy Assistant Secretary of Defense for Systems Engineering and Principal<br/>Deputy Secretary of Defense for Systems Engineering—Kristen Baldwin (SES), 22</li> <li>Defense MicroElectronics Activity—Dan Marrujo, 22</li> <li>Naval Surface Warfare Center—Brett Hamilton, 23</li> <li>Air Force Office of Special Investigations—Michael Lyden, 23</li> <li>Defense Advanced Research Projects Agency—Kerry Bernstein, 23</li> <li>Day 2—March 17, 2016, 24</li> <li>MITRE Corporation—Harriet Goldman, 24</li> <li>National Defense Industries Association—Holly Dunlap, 25</li> <li>Air Force Space and Missile Systems Center—David Davis, 26</li> <li>Kansas City National Security Campus—Kent Devenport, 26</li> <li>IBM—Bernard Meyerson, 27</li> <li>Day 3—March 18, 2016, 28</li> <li>Institute for Defense Analyses—Brian Cohen, 28</li> <li>National Institute for Standards and Technology—Jon Boyens and Celia Paulsen, 28</li> <li>Intelligence Advanced Research Projects Activity—Carl McCants, 29</li> </ul> | 21 |

# APPENDIXES

| А | Terms of Reference                               | 33 |

|---|--------------------------------------------------|----|

| В | Committee Member Biographies                     | 34 |

| С | Workshop Agenda                                  | 38 |

| D | Workshop Attendees                               | 41 |

| E | Potential Terms of Reference for Follow-on Study | 44 |

| F | Projected Advancements of Existing Technology    | 45 |

Optimizing the Air Force Acquisition Strategy of Secure and Reliable Electronic Components: Proceedings of a Workshop

# Acronyms

| AFOSI | Air Force Office of Special Investigations           |  |  |  |

|-------|------------------------------------------------------|--|--|--|

| ASIC  | application-specific integrated circuit              |  |  |  |

| ASSP  | application-specific standard product                |  |  |  |

| BEOL  | back end of line                                     |  |  |  |

| CFIUS | Committee on Foreign Investment in the United States |  |  |  |

| CNCI  | Comprehensive National Cybersecurity Initiative      |  |  |  |

| COTS  | commercial-off-the-shelf                             |  |  |  |

| CPU   | central processing unit                              |  |  |  |

| DARPA | Defense Advanced Research Projects Agency            |  |  |  |

| DIA   | Defense Intelligence Agency                          |  |  |  |

| DMEA  | Defense MicroElectronics Activity                    |  |  |  |

| DoD   | Department of Defense                                |  |  |  |

| DoDI  | DoD Instruction                                      |  |  |  |

| DRAM  | dynamic random-access memory                         |  |  |  |

| DSP   | digital signal processor                             |  |  |  |

| FEOL  | front end of line                                    |  |  |  |

| FPGA  | field-programmable gate array                        |  |  |  |

| FY    | fiscal year                                          |  |  |  |

| GPU   | graphic processing unit                              |  |  |  |

| HW    | hardware                                             |  |  |  |

| IA    | information assurance                                |  |  |  |

| IARPA | Intelligence Advanced Research Projects Activity     |  |  |  |

| IC    | integrated circuit; Intelligence Community           |  |  |  |

| ICT   | Information and Communications Technology            |  |  |  |

| IP    | intellectual property                                |  |  |  |

| JFAC  | Joint Federated Assurance Center                     |  |  |  |

| KCNSC | Kansas City National Security Campus                 |  |  |  |

| MPU   | multi-core processing unit                           |  |  |  |

| MTO   | Microsystems Technology Office                       |  |  |  |

| NDAA  | National Defense Authorization Act                   |  |  |  |

ACRONYMS

| хи |  |

|----|--|

| NDIA   | National Defense Industry Association                   |

|--------|---------------------------------------------------------|

| NEA    | Nuclear Enterprise Assurance                            |

| NIST   | National Institute of Standards and Technology          |

| NNSA   | National Nuclear Safety Administration                  |

| NSA    | National Security Agency                                |

| NSE    | Nuclear Security Enterprise                             |

| NSS    | National Security Space                                 |

| NSWC   | Naval Surface Warfare Center                            |

| OEM    | original equipment manufacturer                         |

| OSD    | Office of the Secretary of Defense                      |

| PPP    | program protection planning                             |

| R&D    | research and development                                |

| RFP    | request for proposal                                    |

| ROI    | return on investment                                    |

| RSA    | Rivest-Shamir-Adleman                                   |

| SCRM   | Supply Chain Risk Management                            |

| SES    | Senior Executive Service                                |

| SHIELD | Supply Chain Hardware Integrity for Electronics Defense |

| SMC    | Space and Missile Systems Center                        |

| SOC    | system on a chip                                        |

| SP     | Special Publication                                     |

| SRAM   | static random-access memory                             |

| SSE    | Security Systems Engineer                               |

| SWaP   | size, weight, power                                     |

| TAC    | Threat Assessment Center                                |

| TAPO   | Trusted Access Program Office                           |

| TIC    | Trusted Integrated Chips                                |

| WTA    | Weapon Trust Assurance                                  |

# Overview

In 2012, the National Defense Authorization Act (NDAA), section 818, outlined new requirements for industry to serve as the lead in averting counterfeits in the defense supply chain.<sup>1</sup> Subsequently, the House Armed Services Committee, in its report on the Fiscal Year 2016 NDAA, noted that the pending sale of IBM's microprocessor fabrication facilities to Global Foundries created uncertainty about future access of the United States to trusted state-of-the-art microelectronic components and directed the Comptroller General to assess the Department of Defense's (DoD's) actions and measures to address this threat.<sup>2,3,4</sup> In this context, the Deputy Assistant Secretary of the Air Force (Science, Technology, and Engineering) requested that the Air Force Studies Board of the National Research Council<sup>5</sup> convene a workshop to facilitate an open dialogue with leading industry, academic, and government experts to (1) define the current technological and policy challenges with maintaining a reliable and secure source of microelectronic components; (2) review the current state of acquisition processes within the Air Force for acquiring reliable and secure microelectronic components; and (3) explore options for possible business models within the national security complex that would be relevant for the Air Force acquisition community. This report summarizes the results of a workshop held on March 16-18, 2016, in Washington, D.C., which brought together experts from government, industry, academia to address these issues.

#### THE MICROELECTRONICS LANDSCAPE

During the "dawn" of the semiconductor industry in the 1970s, the focus was on ensuring that specific, required functionality was available through the design, fabrication, and production of application-specific integrated circuits (ASICs) and mass produced computer memories. Since then, advances in device speed, increased processing power and throughput, lower electrical power consumption, vast increases in device volume production, and ingenious, complex designs have enabled numerous new applications and enormous improvements. This rate of technological advance is expected to continue and perhaps accelerate as new substrate materials are introduced.<sup>6</sup>

Because electronic components in many national security systems are designed and intended to last for long periods in sometimes in harsh environments, testing to assure that the parts will indeed function properly and reliably, under all conceivable operational conditions, and function only as designed, becomes

http://www.eetimes.com/document.asp?doc\_id=1327029.

<sup>&</sup>lt;sup>1</sup> National Defense Authorization Act for Fiscal Year 2012 (P.L. 112-81).

<sup>&</sup>lt;sup>2</sup> J. Lipsky, "IBM-GlobalFoundries Deal Finalized," *EETimes.com*, July 1, 2015,

<sup>&</sup>lt;sup>3</sup> National Defense Authorization Act for Fiscal Year 2016, H.R.1735, 114th Congress, https://www.congress.gov/bill/114th-congress/house-bill/1735, accessed April 17, 2016.

<sup>&</sup>lt;sup>4</sup> Global Foundries is an international company headquartered in Santa Clara, California. It is owned by the Mubadala Development Company, a wholly-owned investment vehicle of the Government of Abu Dhabi in the United Arab Emirates.

<sup>&</sup>lt;sup>5</sup> Effective July 1, 2015, the institution is called the National Academies of Sciences, Engineering, and Medicine. References in this report to the National Research Council (NRC) are used in a historical context to refer to activities before July 1.

<sup>&</sup>lt;sup>6</sup> A recent Aerospace Corporation study (TOR-2015-00473) included a summary of "Technology Challenges by 2025."

challenging.<sup>7</sup> The design of such tests requires intimate knowledge of the device operation and requires sophisticated testing techniques and equipment. Government program managers, program executive officers, and agency leaders are faced with the choice of either using commercial-off-the-shelf (COTS) devices— which may or may not support their requirements—and accept unknown risks; or they will have to make significant investments in test and certification technologies to validate operating parameters.

Complicating this situation further is the steadily eroding U.S. involvement in the design and manufacture of necessary electronic devices, and a concomitant decrease in domestic expertise and understanding of reliability and the risks to systems associated with such complexity. As a result of this erosion, there may not be a domestic microelectronics workforce capable of generating the required security and reliability information the government would require to appropriately analyze and advise program managers about the attendant system risks of microelectronic components.<sup>8</sup>

#### **ORGANIZATION OF THE WORKSHOP**

Workshop briefings included information on (1) DoD's strategy for acquiring secure and reliable microelectronic components, (2) the needs of the nuclear weapons enterprise, (3) Air Force processes to gather reliable and secure information, (4) Defense MicroElectronics Activity's (DMEA's) new role as the sole manager of the Trusted Access Program Office (TAPO), (5) Defense Advanced Research Projects Agency and Intelligence Advanced Research Projects Activity technology research and development programs to insure that obtained parts are secure, and (6) the important role of standards in the manufacture and testing of secure and reliable microelectronic components. Importantly, briefings by industry shed light on the economics of electronics manufacturing and highlighted the pros and cons of government ownership of trusted foundries.

One of the issues that was raised repeatedly during presentations was the prohibitive cost associated with dedicated state-of-the-art foundries producing secure and reliable microelectronic components for national security systems. A few participants noted that a main reason associated with the high cost of producing these items is the relatively low volume of items required by DoD and the Intelligence Community in comparison with the commercial marketplace. More than one speaker from government and industry noted that without a reasonable market, industry will find it difficult to support a program based entirely on producing low-volume trusted components for government systems. Other participants commented that another barrier for industry support of producing low-volume trusted components for the government is the burdensome accreditation process the government uses to determine whether a potential supplier is trustworthy. For example, DMEA performs an accreditation process via a Cooperative Research and Development Agreement that allows DMEA to work with a potential supplier every 2 years. More than one participant asked the speaker from DMEA why a supplier would not want to be accredited. Several reasons were provided, including cost, return on investment, fear of not passing the screening, and the potential market share not matching a company's business model. Yet another participant commented that, on an anecdotal level, existing trusted suppliers who were not receiving requests for trusted fabrication prior to the IBM/Global Foundries sale are now seeing an increase in inquiries as a result of the sale. Finally, concerns about the burdens on industry associated with the International Traffic in Arms Regulations, as well as the complex U.S. government acquisition and contracting process, were mentioned by more than one participant during the course of the workshop.

<sup>&</sup>lt;sup>7</sup> There are distinct approaches involved when it comes to testing components for security as opposed to testing them for reliability when a suspicious malicious actor is not involved.

<sup>&</sup>lt;sup>8</sup> U.S. Government Accountability Office, *Trusted Defense Microelectronics: Future Access and Capabilities are Uncertain*, GAO-16-185T, Washington, D.C., October 28, 2015.

**OVERVIEW**

#### **REPORT ORGANIZATION**

Chapter 1 provides a broad contextual background that includes challenges related to current government policies and technological advancements in the area of secure and reliable electronic components in government national security systems. Even though attribution to individual speakers or workshop participants is not provided, this section of the report should not be seen as consensus views of the wide representation of views presented throughout the workshop. Chapter 2 goes on to describe the dialogue that occurred at the workshop, followed by Chapter 3, which provides abstracts of speaker presentations. Appendixes are provided at the end of the report and include the following items: (1) workshop terms of reference, (2) brief biographies of the workshop committee members, (3) speakers and attendees list, (4) suggested terms of reference for a follow-on study, and (5) a summary presented by Bernard Meyerson of his thoughts on the projected advancements of existing technology. *This proceedings summarizes the views expressed by individual workshop participants. While the committee is responsible for the overall quality and accuracy of the proceedings as a record of what transpired at the workshop, the views contained in the proceedings are not necessarily those of all workshop participants, the committee, or the National Academies of Sciences, Engineering, and Medicine.*

# **Workshop Context and Issues**

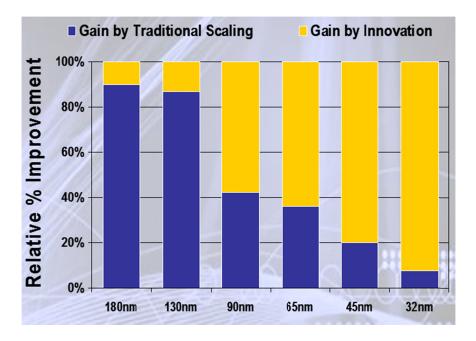

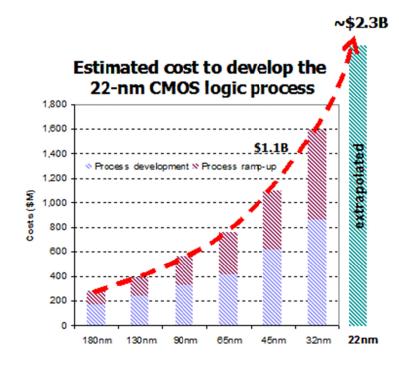

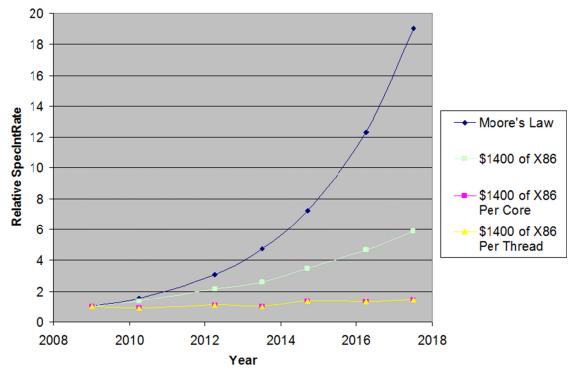

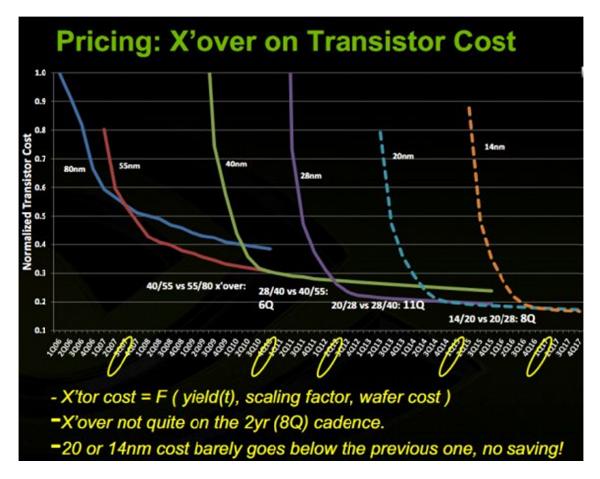

To help provide both context and focus for the workshop, several members of the workshop organizing committee (i.e., Craig Keast, Michael Ettenberg, Robert Latiff, Bernard Meyerson, and Paul Nielsen) framed the workshop discussions by highlighting that advanced electronic devices are critical for all U.S. national security systems, military or intelligence related. The increasing demands for performance of these systems have led to the adoption of ever more sophisticated devices for sensing, computing, control, and other critical functions. For several decades, the technologies for making integrated circuits and microprocessors followed Moore's Law. This "scaling" had the virtuous benefit of making products that were faster, better (i.e., more functional and power efficient), and cheaper, stimulating an enormous information technology industry. Although the cost per transistor steadily decreased, the cost to build foundries for such devices grew in a commensurate fashion; a state-of-the-art foundry costs on the order of \$5 billion to build.<sup>1</sup> Much of the manufacturing of this nature is in Asia. U.S. aircraft, missiles, ships, and ground vehicles, as well as radars and other sensors, depend on access to electronics components that are known to be reliable and to perform as designed. The primary goal of program managers and engineers in national security programs is to assure mission success of weapon systems, and access to reliable and trusted microelectronics are essential to assuring that success.

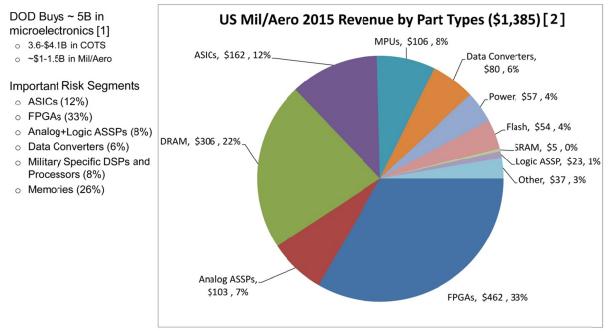

Many of the technologies critical to national security are dependent on leading-edge semiconductors and microelectronic devices that, in many cases, do not have a commercial market (see Figure 1-1). Another school of thought, expressed by one workshop participant, is that leading-edge semiconductors can only be made in high-volume commercial fabrication facilities.

As described by several of the workshop participants (e.g., Kristen Baldwin, Jimmy Goodrich, Terry Lewis, Bernard Meyerson, Celia Paulson, and Dustin Todd) over the 3-day workshop, the acquisition of electronic devices is a complex process that often defies simplification. It includes everything from the sourcing of raw materials, to wafer manufacture, to component design, to software development, to assembly, to testing and certification. The continued and accelerating globalization of the microelectronics industry presents national security program designers with a challenge of how to ensure that electronic components operate as designed. Off-shoring of parts manufacture, decreased Department of Defense (DoD) influence on the industry due to a small comparative demand, and diminished U.S. expertise are all contributing to a growing inability to either understand or assure system security and reliability. The electronics supply chain is complex and has many points within it that can present problems for the ultimate security and reliability of its products. Increasingly, end users demand to know the "pedigree" of the parts they are acquiring for high-priority national security systems. In general, it may be possible to insure greater supply chain trust and reliability of parts by implementing stronger community policies, information sharing on issues and solutions, and coordinated investments in research and development (R&D).

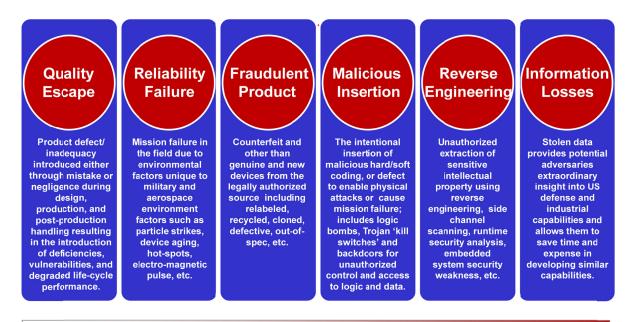

As shown in Figure 1-2, DoD identifies a spectrum of risks to the electronics supply chain. They include (1) quality escapes due to inadequate design or manufacturing quality control; (2) reliability failures; (3) insertion of fraudulent or counterfeit products; (4) insertion of malicious hardware, software, or computer

<sup>&</sup>lt;sup>1</sup> Christopher Mims, "The High Cost of Upholding Moore's Law," *MIT Technology Review*, April 20, 2010.

Sources: [1] IDA Assessment and [2] dataBeans 2014, All data projected for 2015

Application Specific Standard Product (ASSP) - an integrated circuit (IC) dedicated to a specific application market and sold to more than one user. A type of IC with embedded programmable logic, combining digital, mixed-signal and analog products. When sold to a single user, such ICs are ASICs (Gartner)

FIGURE 1-1 Microelectronics in Department of Defense systems. NOTE: Acronyms are defined in the front matter. SOURCE: Brian Cohen, Institute for Defense Analyses, presentation to the workshop on March 18, 2016.

DoD Program Protection focuses on risks posed by malicious actors

FIGURE 1-2 Spectrum of supply chain risks. SOURCE: Kristen Baldwin, Acting Deputy Assistant Secretary of Defense for Systems Engineering and Principal Deputy Assistant Secretary of Defense for Systems Engineering, presentation to the workshop on March 16, 2016. Distribution Statement A—Approved for public release by DOPSR; SR#15S-1541 applies. Distribution is unlimited.

code intended to cause mission failure; (5) reverse engineering of sensitive intellectual property or government information; and (6) outright theft of information that allows adversaries to achieve capabilities they would not otherwise obtain.

DoD's strategy to ensure that critical and sensitive electronics remain viable includes (1) protection of microelectronics designs and intellectual property; (2) advanced hardware analysis capabilities; (3) physical, functional, and design verification and validation; and (4) a new trust model that leverages commercial state-of-the-art capabilities. As an example of this layered approach, the federal government has initiated investments in the development of new, trusted photomask capabilities, tools to enhance the ability to detect flaws, and increased academic and industry research in this area.<sup>2,3</sup> One workshop participant noted that the Trusted Access Program Office (TAPO) also plays a very important function in DoD strategy. TAPO currently manages the trusted part contract with Global Foundries U.S. and is speaking with other fabrication facilities and companies that are manufacturing field-programmable gate arrays (FPGAs) to develop trusted access solutions.

As described by at least one participant during the workshop, prior to the past two decades, the U.S. government had generally enjoyed a mutually beneficial relationship with its supply chain where the government could be assured of acquiring high reliability and state-of-the-art technologies, and suppliers could be assured of benefitting from the results of their R&D investments within a future commercial market. Today, trusted domestic suppliers increasingly find it necessary to forge and accept commitments with what the government may consider non-trusted sources to ensure their own corporate survival within a highly competitive global marketplace. A few participants commented that there are many reasons for this U.S.-supplier marketplace transition. Among them, and perhaps most relevant to the part of the "trusted" microelectronics industry dedicated to the government user, is the near-total loss of on-shore domestic capabilities to fabricate complex, state-of-the-art, highly reliable electronic parts.<sup>4</sup> Another participant commented on the equally important concern stemming from an increasing dependency by the government on the obsolete electronic parts "grey market" where a counterfeit sub-industry has firmly established itself.

Throughout the workshop, several speakers and attendees reinforced the belief within the defense community that the trusted supplier or supply chain is the foundation of assurance for microelectronic parts. Without it, alternative methods to understand the integrity of the product need to be applied and may not achieve the same level of confidence as that won with the trusted supplier/supply chain. However, several participants noted that in lieu of having a trusted supplier or an end-to-end trusted production flow for certain microelectronics, there are efforts underway today to create what are thought to be acceptable alternatives, including broadening the acceptable use of otherwise untrusted sources. Some refer to this concept as establishing "tiers" of trust.<sup>5</sup> Another method to reduce costs for obtaining assurance in lieu of a trusted supply chain that encompasses all electronic components is one that instead focuses the trust requirements only on mission critical parts. Unfortunately, as noted by several participants, more traditional approaches to assuring trust may prevail during more robust financial environments; however, today's budget realities and

<sup>&</sup>lt;sup>2</sup> "A photomask is a tool used for production of components including electronic devices (semiconductors), displays, PCB, and MEMS. It is a master copy for the patterning. Photolithography is used to form PCB circuits and display patterns. Photomasks are used to transfer the patterns on the baseplates. A photomask acts just like "negative film" in photography, and that makes the baseplates "printing paper" (See Filcon Photomask, "What is a Photomask?" http://filcon-photomask.com/en/product/photomask.php, accessed July 7, 2016).

<sup>&</sup>lt;sup>3</sup> "In the event that the GF Trusted Foundry closes, DoD would lose access to trusted photomasks for leading-edge designs" (Kristen Baldwin, Acting Deputy Assistant Secretary of Defense for Systems Engineering and Principal Deputy Assistant Secretary of Defense for Systems Engineering, presentation to the workshop on March 16, 2016).

<sup>&</sup>lt;sup>4</sup> There is U.S.-based, leading-edge manufacturing capability (e.g., Intel). The lack of a leading-edge technology supplier in the United States is more complicated than "they are all off-shore." The current business model requires extremely large volumes, and this does not align with current government procurement practices and programs.

<sup>&</sup>lt;sup>5</sup> The Potomac Institute for Policy Studies is currently undertaking a major 1-year study for DoD to develop such a "tiered" system of trust.

#### WORKSHOP CONTEXT AND ISSUES

limited trusted supplier base for certain devices are forcing managers to take greater programmatic risks.<sup>6</sup> The risks incurred from the acquisition of bad electronic parts from a non-trusted source vary across the spectrum of technical failure modes. Risk impacts that may be realized can be mission-ending, disrupting failures, or life-compromising reliability issues. A poorly managed supply chain offers several points of intrusion or entry for bad actors to insert malicious or counterfeit hardware, software, or firmware.<sup>7</sup> As government systems age, their growing dependency on obsolete parts subjects the buyer to a large, global vendor market of non-OEMs (original equipment manufacturers). An example may be that a vendor is based in the United States with claims of having a desired part, yet may, in fact, reach-back for the parts to unknown sources. Other bad actors may have interests in disrupting a system or compromising its mission life and may have very sophisticated techniques to fool the unsuspecting intake engineer into accepting the product.

An example of an organization that pays attention to electronics obsolescence and to supplier trust accreditation is the Defense MicroElectronics Activity (DMEA). In his presentation and the ensuing discussion, Dan Marrujo from the DMEA described the role of his organization in addressing many of the challenges that were highlighted during the discussions with Kristen Baldwin. DMEA is a key element in the assurance of continued access to obsolete parts and in certifying suppliers for trusted status. One element of the DMEA mission is to re-engineer and manufacture advanced microelectronics parts no longer available to program managers through their industry partners or through other standard commercial sources. Also, DMEA is currently the program manager for the DoD Trusted Foundry Program. Among other tasks, the program negotiates and manages trusted access contracts with state-of-the-art fabrication facilities (e.g., GlobalFoundries U.S.) and accredits sum-of-the-parts microelectronics companies for trust. DMEA accredits suppliers' processes in the areas of integrated circuit design, aggregation, broker, mask manufacturing, foundry, post processing, and packaging/assembly and test services. DMEA is a member of the Joint Federated Assurance Center (JFAC) Working Group. Other members include the Office of the Under Secretary of Defense (Acquisition, Technology, and Logistics), the DoD Chief Information Officer, Military Departments, the Missile Defense Agency, the National Security Agency, the National Reconnaissance Office, and the Defense Information Systems Agency. The JFAC, created by the Deputy Secretary of Defense, identifies, promotes, and facilitates access to hardware and software assurance (i.e., verification and validation) capabilities across the DoD and other federal agencies throughout the system life cycle.)

Several of the workshop participants commented that the ongoing challenge in microelectronics evolution is sheer complexity: logic devices such as application-specific integrated circuits (ASICs) or FPGAs are so complex that determining how to best verify the integrity of the product when the parts may be fabricated in an untrusted foundry has been a more recent, and increasing, concern for programs. ASICs and FPGAs often provide the logic required to drive a critical function. They need to be reliable and tamper-free. Having a trusted supplier and ensuring end-to-end trusted production flow are not achievable goals for some programs. While many studies and innovative technical approaches are under way today to determine methods for achieving some level of confidence that parts will be reliable and can be trusted, no definitive comprehensive approach has been identified to date.

While understanding and attempting to assure the integrity of the supply chain is critical, at the end of the day, designers and system developers need to convince themselves that the delivered electronic products will actually function as advertised, for the length of time needed by the mission, under the conditions expected, and be free from tampering or malicious content. To do so requires rigorous testing and a well-designed certification scheme. Maintaining and assuring the complete integrity of the supply chain is difficult because of the complexity and interconnectedness of the supply chain elements. Items include the raw materials, development tools, facilities and their integrity (production and storage), and the complex machines used to produce parts and their associated programming.

<sup>&</sup>lt;sup>6</sup> One workshop participant noted that there are 72 suppliers on the DMEA accreditation list. This is not a small number, but only a limited number are, in fact, being used for U.S. government needs.

<sup>&</sup>lt;sup>7</sup> See U. Guin, D. DiMase, and M. Tehranipoor, A comprehensive framework for counterfeit defect coverage analysis and detection assessment, *Journal of Electronic Testing* 30(1):25-40.

The contractor community drives, and is driven by, system performance requirements. They need to balance demands for increased performance (e.g., decreased feature size, increased density) with strict security and reliability guidelines. Prime defense contractors have serious concerns about the health of the available industrial base, as well as the ability to obtain quality parts. Significant resources are expended by the industry in quality assurance, as most electronic component suppliers are now off-shore. The supply chain, and the ability to assure its integrity, becomes a very important issue for weapon system developers and electronic component manufacturers. Industry watchers are concerned with an accelerating rate of consolidation and closures that are taking place within the manufacturing sector.

In summary, the workshop presentations and discussions highlighted the observation that the national security electronics industrial base is being pulled in different directions. On the one hand, they are at the mercy of the electronics manufacturers and suppliers. On the other hand, the government program offices are making performance demands, security demands, and reliability demands that the industrial base is increasingly unable to guarantee. The problem is exacerbated by diminishing support by the government for expensive and unique test facilities and inconsistent requirements from the system designers. The industry is looking to the government for leadership and guidance and, in its absence, is having to make tough, sometimes non-optimum, choices. The industry and its ability to supply the kind of high-quality, high-reliability systems needed for their products.

# Workshop Discussions and Key Themes

Over the course of the 3-day workshop, there were numerous topics raised by speakers and brought up during related discussions. These topics and discussions are organized, roughly, according to the workshop terms of reference (provided in Appendix A). Finally, there are contained in each of the following sections certain key themes that arose during the workshop across multiple presentations and associated discussions, and these are highlighted below.

#### CURRENT TECHNOLOGICAL AND GOVERNMENT POLICY CHALLENGES

Current Department of Defense (DoD) policy guidance pertaining to secure and reliable microelectronic components is covered by DoD Instruction (DoDI) 5200.44 and DoDI 4140.67.

Establishes policy and assigns responsibilities to minimize the risk that DoD's warfighting mission capability will be impaired due to vulnerabilities in system design or sabotage or subversion of a system's mission critical functions or critical components by foreign intelligence, terrorists, or other hostile elements.<sup>1</sup>

Establishes policy and assigns responsibilities necessary to prevent the introduction of counterfeit materiel at any level of the DoD supply chain.<sup>2</sup>

The Defense MicroElectronics Activity (DMEA) is the sole manager of the Trusted Access Program Office (TAPO) that is responsible for ensuring that trusted microelectronics are available for U.S. national security systems.<sup>3</sup> The speaker from DMEA noted that his organization is primarily interested in DoDI 5200.44—specifically, the requirement to use trusted foundries and suppliers for application-specific integrated circuits (ASICs). A participant from the Office of the Secretary of Defense noted that DoDI 5200.44 requires and promulgates acquisition programs to use only ASICs that have been designed, fabricated, and packaged by suppliers that have been "trust" accredited by DMEA. Importantly, however, one participant noted that the current government policies only cover ASICs and do not address other commercial-off-the-shelf (COTS) electronic components, which make up the majority of microelectronics used in DoD mission-critical systems. DoDI 5200.44 also authorizes the Air Force Office of Special Investigations (AFOSI) to investigate and provide threat reports upon request. These threat reports are created and disseminated through the Defense Intelligence Agency's (DIA's) Threat Assessment Center (TAC).<sup>4</sup>

<sup>&</sup>lt;sup>1</sup> Department of Defense, "Protection of Mission Critical Functions to Achieve Trusted Systems and Networks (TSN)," DoDI 5200.44, November 5, 2012. http://www.dtic.mil/whs/directives/corres/pdf/520044p.pdf.

<sup>&</sup>lt;sup>2</sup> Department of Defense, "DoD Counterfeit Prevention Policy," DoDI 4140.67, April 26, 2013,

http://www.dtic.mil/whs/directives/corres/pdf/414067p.pdf.

<sup>&</sup>lt;sup>3</sup> The TAPO was established in 2006 based on the recommendations of Defense Science Board, *Task Force on High-Performance Microchip Supply*, 2005, http://www.acq.osd.mil/dsb/reports/ADA435563.pdf.

<sup>&</sup>lt;sup>4</sup> According to the speaker from AFOSI, the Intelligence Community does not have a policy directive equivalent to DoDI 5200.44.

| USD(I)       | USD(I) DoDI 5200.39 - Critical Program Information (CPI) Identification and<br>Protection Within Research, Development, Test, and Evaluation (RDT&E) |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| L&MR         | DoDD 5134.12 Logistics & Materiel Readiness Organization                                                                                             |  |  |  |  |

| DSS          | National Industrial Security Program (NISP) - Executive Order 12829<br>Foreign Ownership, Control or Influence (FOCI)                                |  |  |  |  |

| СЮ           | Protection of Mission Critical Functions to Achieve Trusted Systems and<br>Networks (TSN)DoDI 5200.44                                                |  |  |  |  |

| MIBP         | Ensure robust, secure, resilient, and innovative industrial capabilities upon which the DoD can rely to fulfill the Warfighter's requirement         |  |  |  |  |

| DoDD 5000    | DoDI 5000.02 (7Jan 2015) USD(AT&L):<br>Operation of the Defense Acquisition System                                                                   |  |  |  |  |

| DoDI 4140.01 | Establishes policy and assigns responsibilities for management<br>of materiel across the DoD supply chain.                                           |  |  |  |  |

| Acquisition  | DoDI 5000.02, Jan 7, 2015, Operation of the Defense Acquisition System<br>All of the Above; Affordability; Sequestration, Ind Base, Budgets          |  |  |  |  |

| DLA          | QPL/QML                                                                                                                                              |  |  |  |  |

FIGURE 2-1 Current government policies pertaining to secure and reliable microelectronic components. SOURCE. Dave Davis, Chief Engineer, Air Force Space and Missile Systems Center, presentation to the workshop on March 17, 2016.

The chief engineer from the Air Force Space and Missile System Center (SMC) agreed and affirmed that SMC follows DoDI 5200.44 in the areas of getting DIA TAC reports for risk assessments, counterfeit prevention, and the use of DMEA-accredited ASICs. A DMEA representative noted that there is widespread knowledge of the DoDI 5200.44 policy, but not necessarily the *definition* of the policy. A speaker from the National Defense Industry Association (NDIA) confirmed this view by stating that there is a knowledge gap in government of the requirements of 5200.44 and that there is a need to educate the acquisition community on 5200.44.<sup>5</sup> Finally, Figure 2-1 provides examples of the organizations and policies addressing the multiple missions and solutions required to address integrity assurance in microelectronic components used in DoD national security and weapons systems, according to multiple participants.

Finally, a key limitation with respect to government policies in the area of microelectronics is the time involved in drafting and implementing new DoD-wide policies—specifically, it can take up to 2 years to write and 2 years to implement new policies, according to a participant from the Office of the Secretary of Defense (OSD). At the same time, this participant agreed that more guidance in this area will help.

In addition to DoDI 4140.67 and DoDI 5200.44, DoDI 5000.02 requires government and industry program managers to employ system security engineering and prepare and maintain a program protection plan (PPP) throughout the acquisition life cycle of a weapon system.<sup>6</sup> According to the speaker from OSD, a PPP requires the identification of critical components in a weapon system and associated risk assessment based on threats, vulnerabilities, and mission criticality. According to the speaker from SMC, they have been

<sup>&</sup>lt;sup>5</sup> The following section provides examples for better government and industry collaboration.

<sup>&</sup>lt;sup>6</sup> Department of Defense, "Operation of the Defense Acquisition System," DoDI 5000.02, January 7, 2015, http://www.dtic.mil/whs/directives/corres/pdf/500002p.pdf.

performing rigorous program protection and countermeasures of the supply chain out of necessity for decades, due to the demands of space systems. Lessons learned from SMC's approach to monitoring suppliers may be applicable to others, including the Joint Federated Assurance Center (JFAC). In response to recent releases where the DoD, NDIA, and the National Institute of Standards and Technology now specify that systems engineers are to provide program protection planning, the speaker noted that SMC's systems engineers have historically performed this function. The speaker noted that requirements call for a security systems engineer (SSE) who performs the oversight of the program protection effort and is aligned with most of the activities currently being performed by SMC systems engineers.

Lastly, embedded systems were noted by multiple participants to be the next big policy issue in the area of secure and reliable microelectronics. The issue is that third-party providers who supply the embedded systems are not scrutinized by the DoD program protection policies being imposed on the discrete component providers. An example that was discussed during the presentation from AFOSI related that the provenance and design documentation, which is considered intellectual property (IP) by the owners of the embedded systems, is rarely provided. This results in components from suppliers that are unspecified to DoD being placed in systems to perform the most critical functions—for example, random number generators. In fact, the majority of microprocessor design products may be from third-party providers.<sup>7</sup>

#### Key Theme 1—DoDI 5200.44

As noted by multiple speakers and participants (e.g., Kristen Baldwin, Daniel Marrujo, and Michael Lyden), DoDI 5200.44 has had a big impact on DoD's approach to Supply Chain Risk Management (SCRM), including (1) enforcing an updated approach to program protection planning; (2) expanding the mission of DMEA; (3) requiring ASICs to be supplied by a trusted foundry; (4) enabling AFOSI to investigate domestic companies and U.S. persons for supply chain threats; (5) requiring testing to evaluate the trustworthiness of hardware and software components; and (6) requiring more rigor in the prevention and detection of counterfeits.

# Key Theme 2—Program Protection Policies

Several presentations (e.g., David Davis, Kent Devenport, Holly Dunlap, John Boyens, and Celia Paulson) revealed that program protection imposed by "top down" policy requires "bottom up" implementation in order for the intent of integrating trust, through verifiable confidence in the integrity of the hardware, firmware, and software components, to be realized. The acquisition reality is that if a fool-proof trusted component was provided, who would be required to use it and by what evidence could it be accepted if not documented by these policies and processes?

<sup>&</sup>lt;sup>7</sup> Microprocessors are a security concern because of the impact they have on system operations, and the design complexity involved, which makes detection of hidden or unwanted functions to be extremely difficult. But there are many other complex devices vulnerable as well, such as FPGAs, ASICs, memory, and random number generators, which play a crucial role in intense computations, such as cryptographic functions.

#### AIR FORCE ACQUISITION STRATEGY OF SECURE AND RELIABLE ELECTRONIC COMPONENTS

### **Current Technology Capabilities to Detect Fraud and Counterfeits**

Counterfeit and clone components are increasingly an issue that the DoD is facing with respect to secure and reliable microelectronics and were the main topics addressed by speakers from AFOSI and the Naval Surface Warfare Center (NSWC). According to presentations, the United States is losing critical IP due to globalization. Key issues the government is facing include (1) clones fabricated in unknown foundries that mimic the operation of authentic parts and (2) replications derived from stolen IP that instead are reverseengineered *with potentially altered function*. A participant noted that the examples shown in the presentations were of older technologies and asked if counterfeiting is more of an issue with older technologies. The speaker from NSWC replied that counterfeiters are rapidly keeping up with advances in technology. Relatedly, the speaker from AFOSI noted that the Air Force is the largest consumer of old and obsolete technologies and that there are no parts that are beyond interest of counterfeiters. Upwards of 50 percent of Air Force sustainment parts originate in the grey market.

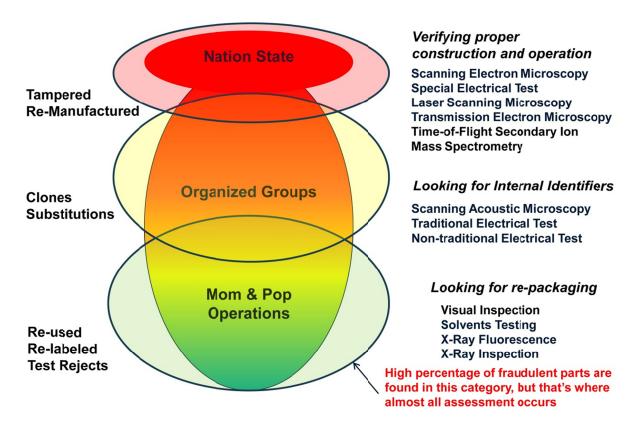

Pertaining to the issues raised in the NSWC presentation, there is inherent risk in looking for counterfeits due to false positive test results that have been observed in some test methods. Some participants noted that variations in chip measurements are criteria for binning of chips per performance measured (an accepted practice). However, these participants noted that measuring these variations is not a criteria for detection of counterfeits, making detection of real counterfeits difficult. The speaker from NSWC cited other methods that are more reliable indicators of counterfeits, such as principal component analysis and vector impedance measurements (see Figure 2-2).<sup>8</sup> The participants from the Department of Energy's Kansas City National Security Campus (KCNSC) stated that Sandia National Laboratories performs all of the testing for Nuclear Enterprise Assurance. One participant stated that establishing the trustworthiness of field-programmable gate arrays (FPGAs) presents multiple concerns, including the following: (1) threats due to malicious insertion, (2) vulnerabilities in programming, (3) complexity in detection methods, and (4) prominence of counterfeits. Another participant commented that a lot of the verification and evaluation tools used for space systems are classified and asked, How can we share these with the broader community and industry? A participant replied that DoD is working on a classification guide for the JFAC for how to share information on vulnerabilities.

Counterfeit parts are easier to make and sell because they do not necessarily have to work in the system under all conditions, as did the original part. They could also contain circuitry that has malicious content that can be activated at some point in the future. The speaker from NSWC noted that, while there are a large number of physical investigative techniques, ranging from simple visual inspection through destructive analysis using scanning electron microscopy, this is a slow and expensive process because it requires having knowledge of the intended design, the use of "golden units" for comparison, and extensive training. Having knowledge of the origin of parts is preferred because it provides legitimacy to the claim of authenticity. Program managers can avoid purchasing parts from after-market suppliers and distributors, however, with system lifetime buys of mission-critical parts at the outset of a program, which enables procurement from the original component manufacturers (OEMs) during production of those parts.

Many workshop participants were encouraged by the innovative and promising initiatives that the Defense Advanced Research Projects Agency (DARPA) either had under way or was starting to ensure the provenance of future integrated circuit parts. For example, the Supply Chain Hardware Integrity for Electronics Defense (SHIELD) program (a taggant) is intended to impose a cost and time asymmetry on the adversary.<sup>9</sup> The taggant is embedded in the package material of the integrated circuit. These will work—as long as they are affixed to legitimate hardware—and are cost effective, but they do not solve the software side of the problem. Software integrity is a more immediate, and probably larger, problem

<sup>&</sup>lt;sup>8</sup> *Impedance* is the effective resistance of an electric circuit or component to alternating current, arising from the combined effects of ohmic resistance and reactance (*Oxford Dictionaries*, http://www.oxforddictionaries.com/us/ definition/american english/impedance, accessed July 7, 2016).

<sup>&</sup>lt;sup>9</sup> A taggant is a unique signature found in an electronic component similar to strips found in currency notes to deter counterfeiters. For additional information on different forms of taggants, see Microtrace, "What is Taggant?," http://www.microtracesolutions.com/taggant-technologies/, accessed June 27, 2016.

FIGURE 2-2 Technological capabilities and approaches to detecting counterfeits. SOURCE: Brett Hamilton, Chief Engineer Trusted Microelectronics, JFAC Hardware Assurance Lead, Global Deterrence and Defense Department/Flight Systems Division, Naval Surface Warfare Center, presentation to the workshop on March 16, 2016.

with weapons systems maintenance than the replacement of obsolete parts. The speaker from DARPA noted that technological solutions to ensure unchanged genuine parts and software are very possible and have the advantage of lower cost and significantly less supply-side disruption compared to bureaucratic policy solutions. In addition, DARPA noted that R&D costs are relatively inexpensive compared to added bureaucracy, and technological solutions are far easier and faster to implement. A key requirement of the DARPA SHIELD program is adoption of this taggant technique by the broader commercial industry. This is a necessary requirement to reach the cost targets and ultimate integration of this technology into the integrated circuit supply chain. Finally, one participant noted that software or hybrid software/hardware design features could help with making sure malware is not inserted in parts that are manufactured totally, or in part, in untrusted fabrication facilities; these same techniques could possibly help in the detection of clone or counterfeit parts. This "dual phenomenology" approach would make it more difficult to defeat techniques to improve trust in the supply chain.<sup>10</sup>

<sup>&</sup>lt;sup>10</sup> Although not specifically detailed during the workshop, the following related concepts were mentioned by the participant: (1) Released firmware and software can be checked for authenticity by cryptographic methods, such as "hash" verification, which would expose any unauthorized changes to the operational code. (2) The technique described above, coupled with on-board hardware logic that would be added, would work in tandem to monitor (each other's) configuration; thus, if either the hardware, software, or firmware were modified, the combined verification check would fail. (3) Counterfeit parts would be exposed since they would not have access to, the pedigree of, or the capability to reproduce these functions.

AIR FORCE ACQUISITION STRATEGY OF SECURE AND RELIABLE ELECTRONIC COMPONENTS

#### Key Theme 3—Emerging Counterfeiting Capabilities

Several presentations (e.g., Kerry Bernstein, Brett Hamilton, and Michael Lyden) conveyed that clones and mimics are a more advanced type of counterfeit capability and an emerging concern because they are harder to detect. Accordingly, current visual inspection and common testing methods will not reveal the lack of performance expected of the authentic component.

#### **CURRENT GOVERNMENT ACQUISITION CHALLENGES**

One participant noted that the acquisition challenges for semiconductor technology can be separated into two divergent classes: (1) Class A, the acquisition of "bleeding edge" silicon technology and designs during its generation, literally at the limits of first-of-a-generation commercial availability and (2) Class B, acquisition of technology typically 3 to 4 generations behind the leading edge, such that the capital costs of obtaining such a fabricator would be a small fraction that of its original value. With these two options in consideration, this participant suggested evaluating the scenarios highlighted in Box 2-1.

A second challenge related to current acquisition processes for acquiring secure and reliable microelectronic components are relationships between government and industry program offices. One participant at the start of the workshop posed the following questions: How do we include and address rolling standards, metrics, and policies or processes, and How can any solutions be incorporated in Air Force acquisition? It was noted by some participants that the government does not necessarily know how to communicate SCRM requirements to industry, especially intelligence data on threats. A senior government leader at the workshop admitted that knowledge of SCRM requirements in government program offices is lacking and that there is a need for an integrated SCRM plan. An industry participant at the workshop strongly believed that discussions between government and industry need to occur before a contract starts and that it is critical to have engineers involved in the decision process, especially because the number of security-relevant SCRM requirements has greatly increased. (Getting these requirements into requests for proposals (RFPs) is critical.)

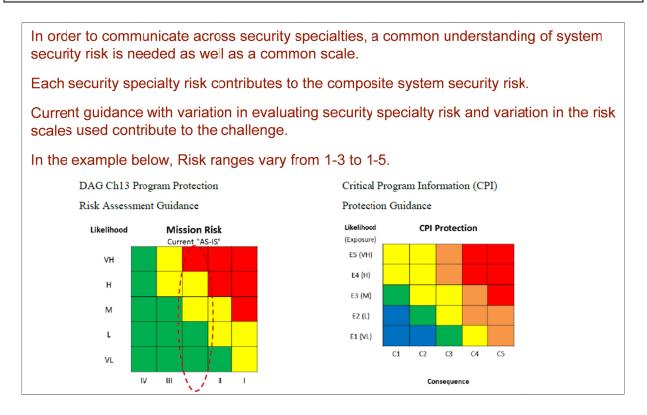

A participant noted that, traditionally, SCRM experts have come up through security fields, not engineering fields, and that the current thrust now is to push SCRM into systems engineering fields and acquisition fields. Another participant stated that the people who are writing the policies and acquisition RFPs also do not have these backgrounds. An industry representative stated that industry cannot do anything unless SCRM requirements are explicit in the contract—for example, common metrics for trust that are already being used by the anti-tamper community (see Figure 2-3).

One speaker on the last day of the workshop noted that, up until the 1990s, military microprocessor capabilities were superior to commercial products and that commercial products lifetimes have since been reduced dramatically. He stated that, once the trend to shorter lifetimes could begin to be observed, the government should have shifted the acquisition process to match the time-to-market shift to COTS products that were being used. A participant then posed a question, What evidence do you see of potential reforms to the acquisition system? The speaker replied that there has been some effort with respect to information systems; with respect to highly specialized defense systems, it is more difficult. A potential area to address a lot of the problems is reform of the acquisition system; although, as noted by another participant, it takes years to fight acquisition bureaucracy and to implement new practices.

WORKSHOP DISCUSSIONS AND KEY THEMES

# BOX 2-1 Potential Technology Acquisition Approaches

## Bernard Meyerson, IBM

- For Class A technology the means by which trusted-by-design components can be deployed through one or more of the following approaches are the following: (1) a split foundry approach, (2) some level of trusted mask and lithography execution, or perhaps, (3) the use of autonomic monitoring of critical component behavior to provide real-time behavioral monitoring and operational assessment of the critical system element. This subset of the study does not propose to evaluate the return on investment (ROI) associated with the Department of Defense (DoD) taking ownership of a state-of-the-art fabricator.

- 2. For Class B technology, which is intended to address the needs of DoD and related agency legacy system component trust and availability, it is conceivable that fabricator ownership would meet the fiscal and technology requirements to fulfill that mission. No such outcome is assumed, but rather it is incumbent on us to perform a rigorous ROI assessment given both the dramatic devaluation of fabricator value as they age, as well as the rising costs and complexities associated with the sourcing of legacy components, the evaluation of their status as to being trusted, and the unavailability of some essential circuitry as such technology becomes obsolete.

FIGURE 2-3 A proposed common government/industry approach to characterizing risk. NOTE: Mission risk cubes are widely used in the Department of Defense (DoD) systems engineering community. Typically, green signifies low risk, followed by yellow for moderate risk, followed by red for the highest risk. DAG, Defense Acquisition Guidebook. SOURCE: Holly Dunlap, Chair, Systems Security Engineering Committee, National Defense Industry Association, presentation to the workshop on March 17, 2016.

A participant noted that policy and processes are needed by the acquisition workforce to ensure that contracts, parts procurement, and methods are put into practice to detect and prevent corrupted components and vulnerabilities from entering the systems' life cycle—and one of the biggest problems is lax enforcement by government program offices of existing policies. The participant went on to specify that the acquisition process and workforce need to be more disciplined in performing program protection to assure system trustworthiness. This rigor needs to be applied to parts procurement guidelines, contracts (RFPs, statements of work, statements of objectives), design, and test. Finally, the participant stated that legacy systems and modernization programs are susceptible to bypassing recent program protection revisions to avoid extensive rework (i.e., cost) in requirements, documentation, and contracting efforts. This leads to perpetuating the fielding of vulnerable systems (which correspondingly have long operational life cycles).

Finally, another participant noted that there is far too much diversity in the rules for how DoD controls the acquisition and disposition of semiconductors and associated electronic assets. For example, in many, if not most, common systems in DoD usage today, there are system elements, such as FPGAs and graphic processing units (GPUs), that can be re-purposed after the fact. Similarly, analog circuitry has similar tuning capabilities. A critical aspect in both validating a system's correct function, as well as maintaining it over time, is the quality and trust of one's test equipment. This participant believed that it is important in any formal assessment of component acquisition that one include considerations as to the trust associated with the test equipment employed over the life of a given system and its components.

#### Key Theme 4—Acquisition System Implementation of DoDI 5200.44

Multiple speakers and participants (e.g., Kristen Baldwin, Brian Cohen, Harriet Goldman, and Daniel Marrujo) noted that the current acquisition system status quo is lacking in the implementation of DoDI 5200.44, which was to provide program protection for threats emanating from the supply chain and vulnerabilities in design. These speakers and participants stated that training, guidance, and security evaluation criteria need to be included in solicitations with metrics. Enforcement is needed at the program level.

#### Key Theme 5—Physical Limits of Current Technology

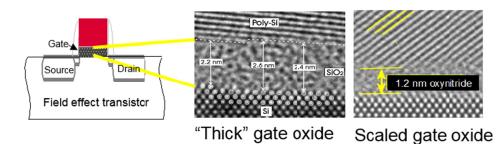

Cutting across multiple presentations (e.g., Kerry Bernstein, Carl McCants, and Bernard Meyerson) was the idea that current technology is at the end of an era as the physical limits of microelectronics have been reached (i.e., traditional scaling based Moore's Law is coming to an end). Although this is a problem for advancement for current foundries, this may be an opportunity to prepare for the next era where trust is a requirement for next-generation components.

# OPTIONS FOR POSSIBLE BUSINESS MODELS WITHIN THE NATIONAL SECURITY COMPLEX

At a strategic level, OSD explained the department's planned long-term investment strategy for trusted microelectronics. The parallel components on this strategy include the following: (1) DoD identifying a commercial supplier of photomasks and building a trusted strategy to procure these; (2) transferring National Security Agency (NSA) TAPO roles and responsibilities to DMEA; (3) improving DoD microelectronics

WORKSHOP DISCUSSIONS AND KEY THEMES

evaluation (test and validation) capabilities; and (4) developing and demonstrating alternative approaches to the trusted foundry model.<sup>11</sup> One participant noted that moving from a trusted hardware model to a trusted software model, which is where the department appears to be heading, is troubling—specifically, software can be made more assured, but not necessarily trusted.

The concept of split manufacturing was raised by multiple speakers as an alternative business model to the current approach by DoD (see Figures 2-4 and 2-5). Split manufacturing involves doing the initial processing steps (front end of line, or FEOL) at one foundry and finishing the fabrication at another foundry (back end of line, or BEOL). One advantage of this approach is that a higher degree of security can be obtained by doing the split earlier in the process of manufacture. The chief engineer from SMC noted that split fabrication is being reviewed by SMC as a possible alternative to loss of the current trusted foundry model.

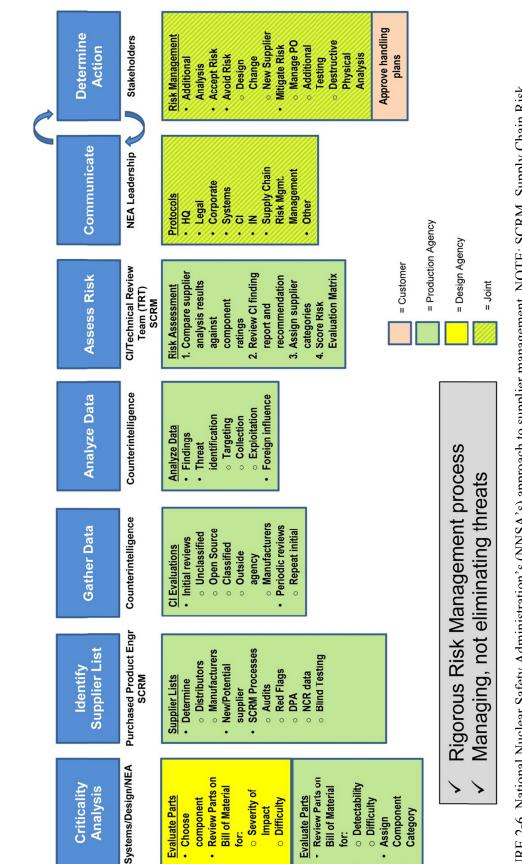

Another possible business model for acquiring secure and reliable microelectronic components is the approach taken by the KCNSC under the Department of Energy, as summarized in Figure 2-6. Unlike the many weapon systems and technologies that DoD is responsible for, the KCNSC is responsible for acquiring and inserting ASICs in nuclear weapon systems only. In a telling remark from the speaker from KCNSC, KCNSC has since borrowed heavily from DoDI 5200.44 while implementing a formal process for SCRM. A question that was asked by one of the participants, which went unanswered, is what DoD can learn from National Nuclear Safety Administration's (NNSA's) approach that is not cost-prohibitive.

- Demonstrate the concept of split-manufacturing of integrated circuits using a state-of-the-art offshore (untrusted) FEOL (Front End of Line) foundry and an onshore (trusted) BEOL (Back End of Line) foundry.

- Perform split at <u>Metal 1 or Metal 2</u> split at <u>Metal 4 or</u> <u>higher</u> used in standard split manufacturing.

- Manage PDKs (Process Development Kits) from different foundries.

- Fabricate chips at the 130nm, 65nm and 28nm manufacturing nodes.

- Develop new IC obfuscation layout strategies to protect both functional capability and performance.

- Anticipate and respond to evolving worldwide trends in semiconductor manufacturing.

- New technologies in advanced manufacturing.

- Foundry offerings and consolidation.

- 3D Integration (More-than-Moore).

- Cybersecurity concerns.

FIGURE 2-4 Trusted Integrated Circuit program approach to split manufacturing. SOURCE: Carl McCants, Program Manager, Intelligence Advanced Research Projects Activity, presentation to the workshop on March 18, 2016.

<sup>&</sup>lt;sup>11</sup> Kristen Baldwin, Office of the Secretary of Defense, "Long-term Strategy for DoD Trusted Foundry Needs," presentation to the workshop on March 16, 2016.

| Metrics<br>Technology Node                            |                        | Phase 1A        | Phase 1B                      | Phase 2                       | Phase 3                       |

|-------------------------------------------------------|------------------------|-----------------|-------------------------------|-------------------------------|-------------------------------|

|                                                       |                        | Base<br>(12 mo) | Option<br>Period 1<br>(12 mo) | Option<br>Period 2<br>(18 mo) | Option<br>Period 3<br>(18 mo) |

|                                                       |                        | 130 nm<br>node  | 65 nm<br>node                 | 28 nm<br>node                 | 28 nm<br>node                 |

| Circuit Complexity                                    | Digital                | >10K            | >100K                         | >1M                           | >10M                          |

| (# of transistors)                                    | Analog/Mixed<br>Signal | >100            | >1K                           | >1K                           | >10K                          |